منطق تزویج امیتری

در رشته الکترونیک، منطق تزویج امیتری (ECL) یکی از سریعترین منطقهای ترانزیستوری دوقطبی در مدارهای مجتمع بهشمار میآید. ECL از یک تقویتکننده تفاضلی ترانزیستور پیوندی دوقطبی فوق راه اندازی با ورودی تک سر و جریان امیتری محدود بهره میبرد تا از ناحیه اشباع عملیات و قطع آن جلوگیری شود. وقتی که جریان بین دوپایه جفت تزویج امیتری هدایت شود، ECL را بعضاً منطق current-steering logic, current-mode logic یا current-switch emitter-follower (CSEF) logic میگویند. در منطق تزویج امیتری (ECL)، ترانزیستورها هرگز در حالت اشباع قرار نمیگیرند. ولتاژهای ورودی / خروجی دارای لرزش جزئی (V 0.8) هستند.

مقاومت ورودی بالا و مقاومت خروجی پایین است. در نتیجه، ترانزیستورها به سرعت تغییر حالت میدهند. تاخیرها در گیت کم و گنجایش خروجی (fan out) بالا میباشد. علاوه بر این، دریافت جریان ثابت تقویت کنندههای تفاضلی تاخیرها و جهشهای نامطلوب ولتاژ و نقصهای فنی جزئی را که به دلیل اندوکتانس و ظرفیت خط تغذیه اتفاق میافتد، به حداقل خود میرساند. خروجیهای مکمل با کاهش شمارش وارونگر (معکوس کننده) زمان انتشار مدار کل را کاهش میدهد. عیب اصلی ECL این است که همواره گیتها در حال دریافت جریان هستند. این بدان معنی است که ECL نسبت به سایر منطقها به برق خیلی بیشتری نیاز دارد. معادل منطق تزویج امیتری حاصل از FETها منطق همراه منبع (Coupled logic ـ source) یا SCFL نامیده میشود. نوعی از ECL که در آن همه مسیرهای سیگنالها و ورودیها گیت تفاضلی هستند، منطق سوئیچ جریان تفاضلی خوانده میشود.

تاریخچه

هانون اس یورک (Hanon s.yourke) مهندس شرکت IBM در ماه آگوست ۱۹۵۶، ECL را اختراع کرد. این منطق که ابتدا منطق هدایت جریان نام داشت، برای کامپیوترهای IBM 7090 و IBM 7094 مورد استفاده قرار میگرفت.

به این منطق مدار حالت جریان نیز میگفتند. از این منطق برای ساخت مدارهای ASIT در کامپیوترهای IBM 360/91 استفاده میشد. سوئیچ جریان یورک تقویتکننده تفاضلی بود که سطوح منطق ورودی آن نسبت به سطوح منطق خروجی اش متفاوت بود. با این حال، در عملیات حالت جریان، سیگنال خروجی شامل سطوح ولتاژی است که حدود سطح مرجع نسبت به سطح مرجع ورودی متفاوت است. در مدل یورک، سطوح مرجع ۲ منطق تا ۳ ولت با هم فرق دارند. در نتیجه، دو نوع مکمل مورد استفاده قرار گرفت:

یک نسخه NPN و یک نسخه PNP. خروجی NPN میتوانست ورودیهای PNP را حرکت دهد و بالعکس. ایرادات آن این است که ولتاژ منبع تغذیه متفاوت بیشتری نیاز است؛ و همچنین هم به ترانزیستور PNP و هم ترانزیستور NPN احتیاج است.

به جای تغییر مراحل NPN و PNP شیوه ترویج دیگری بود که از دیودهای زنر (Zener diodes) و متفاوت برای تغییر سطوح منطق خروجی جهت همسان سازی سطوح منطق ورودی استفاده میکرد. در اوایل دهه ۱۹۶۰ میلادی، مدارهای ECL بر روی مدارهای مجتمع یکپارچه پیاده شد که برای اجرا و عمل کردن منطق دارای یک مرحله ورودی تقویتکننده تفاضلی بود. این مدارها همچنین برای سوق دادن یا تحریک خروجیها و تغییر ولتاژهای خروجی از یک مرحله امیتر پیرو برخوردار بودند طوری که میتوانستند با ورودها سازگار باشند. از مراحل خروجی امیتر پیرو همچنین برای اجرای منطق یا سیمی (orlogic ـ wired) مورد استفاده قرار میگرفت.

شرکت موتورولا در سال ۱۹۶۲ اولین خط تولید مدار مجتمع یکپارچه دیجیتالی خود را معرفی نمود. این شرکت سریهای متفاوتی را تولید کرد.MECL II در سال ۱۹۶۶ میلادی، MECL III در سال ۱۹۶۸ میلادی با زمان انتشار گیت یک نانو ثانیه و آهنگ تغییر وضعیت مداری فلیپ فلاپی ۳۰۰ مگاهرتز، و سری ۱۰۰۰۰ (با مصرف برق کمتر و سرعت لبهای کنترل شده) در سال ۱۹۷۰ از این جملهاند. مصرف برق بالای CCL بدین معنی است که از آن اصولاً زمانیکه سرعت بالا ضروری به نظر میرسد، استفاده شود.

کامپیوترهای بزرگ قدیمی تر مانند Enterprise system / 9000 از اعضای خانواده کامپیوتر ESA/390 شرکت IBM مانند ۱ـ cary و کامپیوترهای نسل اول Amdahl ( کامپیوترهای IbM فعلی از CMOS استفاده میکنند) از ECL استفاده میکردند. کامپیوترهای DEC VAX 8000 نیز از ECL استفاده میکردند.

پیادهسازی و اجرا

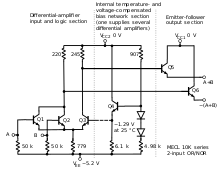

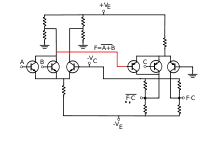

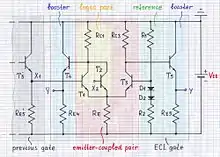

این تصویر نمودار مدار ECL را براساس MECL شرکت موتورولا نشان میدهد. در این شکل، ترانزیستور T5 ترانزیستور خروجی گیت ECL قبلی ای را نشان میدهد که یک سیگنال منطق را برای ترانزیستور ورودی T1 از یک گیت OR/NOR که ورودی دیگر آن T2 است و خروجیهای Y و Y دارد فراهم میکند. تصاویر دیگر عملیات مدار را با در نظر گرفتن آزادسازی بار و توپولوژی جریان با ولتاژ ورودی پایین ("0" Logical) طی انتقال یا گذار و با ولتاژ ورودی بالا ("1" Logical) نمایش میدهند.

ECL بر مبنای زوج امیتری است که در این شکل در سمت چپ با رنگ قرمز هاشور خوردهاست. نیمه سمت چپ این زوج (که با رنگ زرد هاشور خورده) شامل دو ترانزیستور ورودی موازی T1 و T2 (گیت نمونه با دو ورودی) است که منطق T3 با یک منبع ولتاژ مرجع محکم شدهاست که با رنگ سبز کم رنگ هاشور خوردهاست: مقسم ولتاژ با جبران گرمایی (یودی R1 و R2 و D1 و D2) و بعضی وقتها امیتری پیرو میانگر (که در تصویر نشان داده شدهاست) در نتیجه، ولتاژهای امیتری نسبتاً ثابت هستند؛ بنابراین، مقاومت امیتری عادی RE تقریباً مانند منبع جریان عمل میکند. ولتاژهای خروجی در مقاومتهای بار کلکتور RC1 و Rc3 به وسیلهٔ امیتری پیروهای T4 و T5 (که با رنگ آبی هاشور خوردهاند) به خروجیهای معکوسکننده یا وارونگر و غیر وارونگر تغییر میکنند. مقاومتهای امیتری خروجی RE4 و RE5 در همه مدلهای ECL بکار نرفتهاست. در بعضی موارد مقاومتهای خروجی خط ۵۰ اهمی بین بیسهای ترانزیستورهای ورودی متصل شده و ۲- ولت به عنوان مقاومت امیتری عمل میکند.

عملیات

عملیات مدار ECL در زیر با این فرض صورت میگیرد که ولتاژ ورودی برای بیس T1 استفاده شود و ورودی T2 بلااستفاده بوده یا "0" Logical در نظر گرفته شود.

طی گذار یا انتقال، هسته مدار یعنی جفت تزویج امیتری (T3 و T1) به عنوان یک تقویتکننده تفاضل با ورودی تک سری عمل میکند. منبع جریان تزویج امیتری (دم دراز tail ـ long) جریان کل را که از میان دوپایه این جفت عبور میکند، یقین میکند. ولتاژ ورودی شار جریان را به وسیلهٔ ترانزیستورها با تقسیم آن بین دوپایه و در نتیجه هدایت همه آن به یک سمت (زمانیکه به نقطه سوئیچینگ نزدیک نباشد) کنترل میکند.

حاصل یا بهره آن نسبت به حالتهای آخر و زمانیکه مدار سریع کلید میخورد، بیشتر است. با ولتاژ ورودی پایین ("logical"0) یا با ولتاژ ورودی بالا ("logical"1) تقویت کنند. تفاضل بیش از حد رانده یا تحریک میشود. یک ترانزیستور (T3 یا T1) خاموش است و ترانزیستور دیگر (T1 یا T3) در ناحیه خطی فعال قرار داشته و نقش مرحله امیتری عادی را با انحطاط امیتری که همه جریان را جذب میکند و باعث از بین رفتن ترانزیستور خاموش میشود، ایفا میکند.

ترانزیستور فعال دارای باری با مقاومت امیتری نسبتاً بالا است که پسخورد (feed back) منفی قابل توجهای (انحطاط امیتری) را به نمایش میگذارد. برای پیشگیری از اشباع ترانزیستور فعال طوری که زمان نفوذش بازیافت حالت اشباع را کند میسازد و در تأخیر منطق دخیل نیست، مقاومتهای امیتری و کلکتور طوری انتخاب میشود که با بیشینه ولتاژ ورودی، یک مقدار ولتاژ در ترانزیستور باقی خواهد ماند. بهره پسماند کم (1 <RE / RC = K) است. مدار نسبت به تغییرات ولتاژ ورودی حساس نیست و ترانزیستور در ناحیه خطی فعال ثابت باقی میماند. مقاومت ورودی به خاطر پسخورد منفی سری بالا میباشد. ترانزیستور خاموش اتصال بین ورودی و خروجی اش را از بین میبرد. در نتیجه، ولتاژ ورودی آن بر روی ولتاژ خروجی تأثیر نمیگذارد. مقاومت ورودی بار دیگر بالا است زیرا پیوند یا اتصال امیتری بیس خاموش است.

ویژگیها

از ویژگیهای مهم خانواده ECL این است که جریان زیاد تقریباً ثابت است و اصولاً به حالت مدار بستگی ندارد. این بدان معنا است که مدارهای ECL، بر خلاف بسیاری از انواع منطقهای دیگر نسبتاً نویز کمی تولید میکنند. در اپلیکیشنهای رمزگذاری، مدارهای ECL در مقابل حملات کانال جانبی مانند تحلیل توان تفاضلی (differential power analysis) کمتر آسیب پذیرند. زمان انتشار (Propagation delay) در این آرایش کمتر از یک نانو ثانیه است. این امر باعث میشود که از آن سالیان سال به عنوان سریعترین خانواده منطق استفاده شود.

منابع تغذیه و سطوح منطق

مدارهای ECL در مقایسه با سایر خانوادههای مدارهای منطقی که در آنها پایانه منفی تغذیه به زمین متصل است، معمولاً با منابع تغذیه منفی (پایانه مثبت تغذیه یا منبع به زمین متصل است) کار میکنند.

این امر اصولاً برای به حداقل رساندن تأثیر تغییرات با نوسانات منبع تغذیه سطوح منطق اتفاق میافتد زیرا ECL نسبت به سر و صدای VCC حساس و نسبت به سر و صدای VeE نسبتاً مصون است. از آنجائیکه زمین باید با ثباتترین ولتاژ در یک سیستم باشد، ECL با بار مثبت زمین تعیین میشود. در این اتصال، زمانیکه ولتاژ منبع تغییر میکند، کاهش ولتاژ در سر تا سر مقاومتهای کلکتور کمی تغییر میکند (در مورد منبع جریان ثابت امیتر، تغییری صورت نمیگیرد). زمانیکه مقاومتهای کلکتور محکم به زمین متصل هستند، ولتاژهای خروجی کم یا به کندی جابجا میشوند (یا اصلاً حرکت نمیکنند). اگر پایانه منفی منبع تغذیه به زمین متصل باشد، مقاومتهای کلکتور به ریل مثبت متصل خواهد بود. چون افت ولتاژ ثابت در سراسر مقاومتهای کلکتور جزئی است (یا اصلاً تغییری نمیکند) ولتاژهای خروجی از نوسانات ولتاژ منبع پیروی میکنند و دو بخش مدار به عنوان تعویضکننده سطح جریان ثابت عمل میکنند. در این صورت، مقسم ولتاژ R2 ـ R1 تغییرات ولتاژ را تا حدودی جبران میکند. منبع تغذیه مثبت عیب دیگری هم دارد. آن نقص این است که ولتاژهای خروجی در مقابل پیشینه ولتاژ ثابت بالا (V 3/9+) خیلی کم (V 0/4 +-) تغییر میکنند یا دچار نوسان میشوند. دلیل دیگر استفاده از منبع تغذیه مثبت محافظت از ترانزیستورهای خروجی در مقابل اتصال کوتاه ناگهانی است که بین خروجی و زمین به وجود میآید (ولی خروجیها در مقابل اتصال کوتاه با ریل منفی مصون نیستند).

مقدار ولتاژ تغذیه طوری انتخاب میشود که جریان کافی از میان دیودهای جبرانکننده D1 و D2 عبور کند و افت ولتاژ در سرتاسر مقاومت امیتری عادی یا معمولی RE کافی است. مدارهای ECL موجود در بازار آزاد که معمولاً با سطوح منطق کار میکنند با دیگر خانوادهها سازگاری ندارند. این بدان معنی است که عملیات بین ECL و سایر خانواده مدارهای منطقی مانند خانواده معروف TTL به مدارهای میانجی اضافی احتیاج دارند. این حقیقت که سطوح منطق پایین و بالا نسبتاً نزدیک هم هستند بدین معنی است که ECL از سر و صداهای جزئی برخوردار است که این موضوع خود یک مشکل محسوب میشود.

فقط یک شرکت یعنی IBM مدارهای ECL را برای استفاده محصولات خود تولید میکند.

PECL

منطق تزویج امیتری؛ PECL) positive emitter – coupled logic) یا pseudo – ECL نسخه پیشرفته ECL است؛ که به جای منبع V 5/2 منفی از منبع V5 مثبت استفاده میکند. منطق تزویج امیتری مثبت ولتاژ پایین (LVPECL) نوع بهینه PECL است که به جای منبع V5 از منبع V 3/3 مثبت استفاده میکند. PECL و LVPECL سیستمهای سیگنال تفاضلی هستند که اصولاً در مدارهای دارای سرعت بالا و توزیع زمانی به کار میروند.

سطوح منطق

| نوع | Vee | Vlow | Vhigh | Vcc | Vcm |

|---|---|---|---|---|---|

| PECL | GND | 3.4 V | 4.2 V | 5.0 V | |

| LVPECL | GND | 1.6 V | 2.4 V | 3.3 V | 2.0 V |