چکش ردیفی

چکش ردیفی Row hammer (که به صورت rowhammer نیز نوشته میشود) یک سوء استفاده امنیتی است که از یک اثر جانبی ناخواسته و نامطلوب در حافظه تصادفی پویا (DRAM) استفاده میکند که در آن سلولهای حافظه شارژ بین خود را با تعامل با یکدیگر نشت میدهند. در این حالت احتمال نشت یا تغییر اطلاعات در ردیفهای مجاور ردیفی که بهطور مستقیم به آن دسترسی داریم وجود دارد. عدم ایزوله بودن سلولهای حافظه DRAM نسبت به یکدیگر بخاطر تراکم بالای سلول در DRAMهای مدرن میباشد و میتوان با یک سری الگوهای خاص دسترسی به حافظه به صورت سریع و متناوب چندین بار به یک ردیف از حافظه دسترسی داشت که این در حمله rowhammer باعث میشود سلول به اندازه کافی در یک بازه نشت اطلاعات داشته باشد.[1][2][3]

اثر چکش ردیفی در برخی از مزایای افزایش امنیت سیستمهای کامپیوتری استفاده شدهاست[4][5][6][2]و همچنین در حملات مبتنی بر شبکه از لحاظ نظری در ارتباط سریع شبکه بین مهاجم و قربانی امکانپذیر است.[7][8]

تکنیکهای مختلف مبتنی بر سختافزار برای جلوگیری از وقوع اثر rowhammer از جمله پشتیبانی مورد نیاز در برخی از پردازشگرها و انواع حافظه DRAM وجود دارند.[9][10] rowhammer به ندرت یا هرگز بر روی DDR و DDR2 تأثیر نمیگذارد و روی DDR3 و DDR4 تأثیر زیادی دارد.

سابقه

در RAM پویا(DRAM)، هر بیت از دادههای ذخیرهشده، یک سلول حافظه جداگانه را اشغال میکند که به صورت الکتریکی با یک خازن و یک ترانزیستور اجرا میشود. حالت شارژ خازن (شارژ شده یا دشارژ) همان چیزی است که معین میکند که آیا یک سلول حافظه "۱" یا "۰" به عنوان یک مقدار دودویی ذخیره میکند. تعداد بسیار زیادی از سلولهای حافظه DRAM به مدارهای مجتمع متصل میشوند همراه با یک سری منطق اضافی که سلولها را برای اهداف خواندن، نوشتن، و بازنویسی دادهها سازماندهی میکند.[11][12]

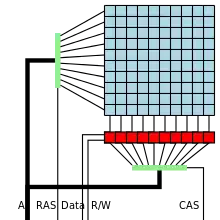

سلولهای حافظه (مربعهای آبی در تصویر) بیشتر به شکل ماتریسها سازماندهی و از طریق سطرها و ستونها آدرس دهی میشوند. یک آدرس حافظه که برای یک ماتریس استفاده میشود به آدرس سطر و ستون تقسیم میشود، که به وسیله آدرس سطر و سپس آدرس ستون به ترتیب پردازش میشوند (در تصویر، به ترتیب مستطیلهای عمودی و افقی سبز نشان داده شدهاست). یک آدرس ردیف، ردیف را برای یک عملیات خواندن انتخاب میکند (به عنوان فعالسازی ردیف نیز شناخته میشود)، بیت از تمام سلولهای موجود در ردیف به تقویت کنندههای حس منتقل میشود که بافر ردیف را تشکیل میدهند (مربعهای قرمز در تصویر) که در آن بیت دقیق با استفاده از آدرس ستون انتخاب میشود. در نتیجه، عملیاتهای خواندن دارای یک ماهیت مخرب هستند، زیرا طراحی DRAM به سلولهای حافظه نیاز دارد تا پس از آنکه مقادیر آنها با انتقال بار سلول به بافر سطر خوانده شد، بازنویسی شوند. عملیات نوشتن آدرسها را به روشی مشابه رمزگشایی میکند، اما در نتیجه دراین طراحی باید تمام ردیفها بازنویسی شوند تا مقدار یک بیت واحد تغییر یابد.[1][2][3][11][12][13]

در نتیجه ذخیرهسازی بیتهای داده با استفاده از خازن که سرعت تخلیه طبیعی دارند، باعث میشود DRAM حافظه خود را در طول زمان از دست بدهد و نیاز به بازنویسی مجدد همه سلولهای حافظه دارند، که فرآیندی است که به عنوان دوبارهسازی شناخته میشود. در نتیجه دیگر طراحی، حافظه DRAM مستعد تغییرات تصادفی در دادههای ذخیرهشدهاست که به خطاهای حافظه نرم و ویژگی پرتوهای کیهانی و دلایل دیگر شناخته میشوند. تکنیکهای مختلفی وجود دارند که خطاهای حافظه نرم را خنثی و قابلیت اطمینان DRAMرا بهبود میبخشد که حافظه تصحیح خطا (ECC)و انواع پیشرفته آن (مانند حافظه lockstep)اغلب مورد استفاده قرار میگیرند.[14]

مرور

افزایش تراکم مدارهای مجتمع DRAM (ICs) باعث شدهاست که سلولهای حافظه کوچکتر از نظر فیزیکی قادر به ذخیره بارهای کوچکتر باشند، که این منجر به کاهش حاشیه نویز عملیاتی، افزایش سرعت تعامل الکترومغناطیسی بین سلولهای حافظه و احتمال از دست رفتن بیشتر دادهها میشود. در نتیجه، خطاهای اختلال مشاهده میشود که توسط سلولهایی که در عملکرد یکدیگر دخالت میکنند ایجاد میشوند و به صورت تغییرات تصادفی در مقادیر بیتهای ذخیرهشده در سلولهای حافظه قرار میگیرند. آگاهی از خطاهای اختلال به اوایل دهه ۱۹۷۰ و اینتل ۱۱۰۳ بعنوان اولین DRAM در دسترس جامعه بازمیگردد؛ از آن زمان سازندگان DRAMها تکنیکهای مختلفی را برای مقابله با خطاهای اختلال، مانند بهبود انزوای بین سلولها و انجام آزمایش تولید بکار گرفتهاند. با این حال، محققان در یک تجزیه و تحلیل در سال ۲۰۱۴ ثابت کردند که تراشههای DDR3 SDRAM تجاری موجود در سالهای ۲۰۱۲ و ۲۰۱۳ مستعد خطاهای مزاحم هستند، در حالی که با استفاده از اصطلاح چکش ردیف برای نامگذاری عوارض جانبی مرتبط با آن که منجر به مشاهده تلنگرهای بیت شدهاست در حالی که از چکش ردیفی برای نامگذاری اثر جانبی مربوطه استفاده میشود که منجر به پرش بیت میشود.[1][3][15]

دلایل برای اثر چکش ردیفی در حافظه DDR3[16] در درجه اول به تراکم بالای سلولهای حافظه و نتایج تعاملات مرتبط بین سلولها نسبت داده میشود، در حالی که فعالسازیهای سریع DRAM به عنوان علت اصلی تعیین شدهاست. فعال سازیهای مکرر ردیف باعث نوسان ولتاژ در خطوط انتخاب ردیف مرتبط میشود، که مشاهده شدهاست که نرخهای تخلیه بیش از حد مجاز در خازنها متعلق به ردیفهای حافظه مجاور است، که ردیفهای قربانی نامیده میشوند. اگر سلولهای حافظه آسیب دیده قبل از اینکه شارژ زیادی از دست ندهند تجدید نشوند، خطاهای مزاحم رخ میدهد. آزمایشها نشان میدهند که یک خطای اختلال ممکن است پس از انجام هر گونه نمایش در حدود ۱۳۹٬۰۰۰ دسترسیهای حافظه بعدی (با تخلیه حافظه نهان) مشاهده شود و این که یک سلول حافظه در هر ۱۷۰۰ سلول ممکن است در معرض خطر باشد. این تستها همچنین نشان میدهند که میزان خطای اختلال بهطور قابلتوجهی با افزایش دمای محیط تحتتاثیر قرار نمیگیرد، در حالی که به محتوای واقعی DRAM بستگی دارد، زیرا الگوهای بیت خاصی منجر به خطای اختلال در دماهای بالاتر میشود.[1][2][15][17]

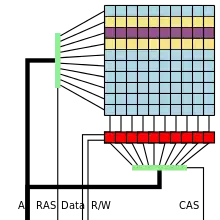

نوعی به نام double-sided hammering شامل فعال سازی هدفمند دو ردیف DRAM در اطراف یک ردیف قربانی است. در تصویر ارائه شده در این بخش، این نوع میتواند هر دو ردیف زرد را با هدف القاء پرشهای بیت در ردیف بنفش فعال کند، که در این حالت، ردیف قربانی خواهد بود. آزمایشات نشان میدهد که این روش ممکن است منجر به میزان قابل توجهی بالاتر از خطاهای مزاحم شود، در مقایسه با نوعی که تنها یکی از ردیفهای DRAM همسایه ردیف قربانی را فعال میکند.[4][18][19]

کاهش

روشهای مختلف برای تشخیص موفق، پیشگیری، اصلاح یا کاهش اثر چکش ردیفی وجود دارد. آزمایشات نشان میدهد که راه حلهای ساده ECC، ارائه قابلیتهای اصلاح یک خطا و قابلیت تشخیص دو خطا (SEC DED)، قادر به اصلاح یا تشخیص همه خطاهای مزاحم مشاهده شده نیستند زیرا برخی از آنها شامل بیش از دو بیت پرش در هر کلمه حافظه میشوند.[1][15] همچنین سه بیت خطا مانع از تغییر ECC میشود.[20][21]

یک راهحل موثرتر دوباره نویسی بیشتر حافظه با فاصلههای متناوب کوتاه از ۶۴ میلی ثانیه معمولی است. اما این روش منجر به مصرف بیشتر انرژی و افزایش پردازنده میشود. برخی از فروشندگان به آپدیتهای سیستم عامل میپردازند که این نوع کاهش را پیادهسازی میکنند.[22] یکی از اقدامات پیچیدهتر پیشگیری ردیفهای حافظه که غالباً به آنها دسترسی داریم را پیدا میکنند و فعالانه ردیفهای همسایه آنها را بازنویسی میکند.[1][23]

از زمان انتشار پل «آی وی»(Ivy Bridge microarchitecture)، پردازندههای Xeon از این اصطلاح شبه هدف بازنویسی ردیف(pTRR)پشتیبانی میکنند؛ که میتوان از آنها در ترکیب با DDR3های حافظه میانی دوگانه با قابلیت دوگانه - دوگانه (DIMMs)برای کاهش اثر چکش ردیفی ناشی از ردیفهای قربانی احتمالی بهینه استفاده کرد. بدون تأثیر منفی بر عملکرد یا مصرف توان. هنگامی که با DIMMs مورد استفاده قرار میگیرد، این پردازندهها با استفاده از افت پیشفرض، در دو برابر فرکانس معمول، که منجر به تأخیر دسترسی حافظه بالاتر میشوند و ممکن است پهنای باند حافظه را تا ۴–۲٪ کاهش دهند، بازسازی میکنند.[9]

استاندارد حافظه متحرک LPDDR۴ که توسط JEDEC[24] منتشر شد شامل پشتیبانی سختافزار اختیاری برای بازیابی ردیف هدف نامیده میشود (TRR)که از تأثیر چکش ردیفی بدون تأثیر منفی بر عملکرد یا مصرف انرژی جلوگیری میکند.[10][25][26]علاوه بر این، برخی از تولیدکنندگان TRR را در محصولات DDR4 خود پیادهسازی میکنند[27][28]اگرچه جزئی از استاندارد حافظه DDR4 نیست که توسط JEDEC منتشر شدهاست.[29] از طریق داخلی، TRR با شمارش تعداد فعال سازیهای ردیف و مقایسه آن در برابر تعداد پیش تعریف شده حداکثر فعال سازی تراشه (MAC) و مقادیر حداکثر فعال کننده پنجره (tMAW)، ردیفهای قربانی احتمالی را شناسایی میکند و این سطرها را برای جلوگیری از پرش بیت بازنویسی میکند. مقدار MAC حداکثر تعداد کل فعال سازیهای ردیفی است که ممکن است در یک بازه زمانی مشخص بر روی یک ردیف DRAM خاص مشاهده شود که مساوی یا کوتاهتر از زمان tMAW زمان قبل از ردیفهای همسایه آن به عنوان ردیفهای قربانی است. اگر مجموع فعال سازیهای ردیف برای دو ردیف همسایه خود به حد MAC برسد در پنجره زمان tMAW میتواند TRR را نیز به عنوان یک ردیف قربانی مشخص کند.[24][30]

به دلیل ضرورت تعداد زیاد فعالیتهای ردیف DRAM که به سرعت انجام میشود، بهرهبرداری از چکش ردیفی تعداد زیادی از دسترسیهای حافظه را صادر میکند که باعث از دست رفتن حافظه پنهان میشود؛ که با نظارت بر نرخ خطای حافظه نهان برای پیکهای غیر معمول با استفاده از شمارنده عملکرد سختافزاری تشخیص داده میشود.[6][31]

نسخه ۵٫۰ از نرمافزار تشخیص حافظه MemTest86، که در ۳ دسامبر ۲۰۱۳ منتشر شد، یک تست چکش ردیفی را اضافه کرد که بررسی میکند که آیا RAM کامپیوتر مستعد خطاهای آشفتگی است یا نه.[32]

مفاهیم

محافظت از حافظه، به عنوان روشی برای جلوگیری از دسترسی فرایندها به حافظه که به هریک از آنها اختصاص نیافتهاست، یکی از مفاهیم پشت اکثر سیستم عاملهای مدرن است. با استفاده از حفاظت از حافظه در ترکیب با مکانیزمهای مرتبط با امنیت مانند حلقههای محافظ، امکان جداسازی امتیاز بین فرایندها وجود دارد، که در آن برنامهها و سیستمهای کامپیوتری به بخشهایی محدود میشوند که نیاز دارند یک کار خاص را انجام دهند. استفاده از تفکیکپذیری میتواند میزان آسیب احتمالی ناشی از حملات امنیتی کامپیوتر را با محدود کردن اثرات آنها به قسمتهای خاص سیستم کاهش داد.[33][34]

خطاهای اخلال (توضیح دادهشده در بخش بالا) بهطور مؤثر لایههای مختلف حفاظت از حافظه را در سطح بسیار پایین سختافزار شکست میدهد، عملاً ایجاد یک نوع بردار حمله منحصر به فرد که به فرایندها اجازه میدهد تا محتویات بخشهای اختیاری حافظه اصلی را با دستکاری مستقیم سختافزار اصلی تغییر دهند.[2][6][18][35] در مقایسه، بردارهای حمله مرسوم مانند سرریزهای بافر با هدف سوء استفاده از مکانیسمهای محافظت در سطح نرمافزار، با سوء استفاده از اشتباهات مختلف برنامهنویسی برای دستیابی به تغییرات محتوای اصلی حافظه اصلی غیرقابل دسترسی هستند.[36]

بهرهبرداری

تحقیقات اولیه در مورد اثر چکش ردیفی، که در ژوئن سال ۲۰۱۴ منتشر شد، ماهیت خطاهای مزاحم را تشریح کرد و پتانسیل ساخت حمله را نشان داد، اما هیچ نمونه ای از سوء استفاده از امنیت کاری ارائه نکرد.[1] مقاله تحقیقاتی بعدی در اکتبر ۲۰۱۴ به وجود هر گونه مسایل مربوط به امنیت ناشی از اثر چکش ردیفی هیچ اشاره ای نکرد.[16]

در تاریخ ۹ مارس ۲۰۱۵، پروژه Zero گوگل دو بهرهبرداری از امتیازات کاری را براساس اثر چکش ردیفی را با ایجاد ماهیت بهرهبرداری خود در معماری x86-64 فاش کرد. یکی از استفادههای آشکار کننده مکانیسم گوگل (NaCl)گوگل (NaCl)را برای اجرای یک زیرمجموعه محدود از دستورالعمل ماشین ۶۴–۶۴ درون یک sandbox[18]هدف قرار میدهد که از تأثیر چکش ردیفی برای فرار از sandbox استفاده کرده و توانایی فراخوانی سیستم بهطور مستقیم را بدست آورد. این آسیبپذیری NaCl، به عنوان CVE-2015-0565 ردیابی شدهاست، با تغییر NaCl کاهش یافتهاست بنابراین اجازه اجرای دستورالعمل ماشین (Clflush[37](cache line flush را نمیدهد، که قبلاً تصور میشد برای ساختن یک حمله چکش ردیفی مؤثر لازم است.[2][6][35]

دومین بهرهبرداری که توسط پروژه صفر عرضه شد، به عنوان یک فرایند لینوکس بر روی معماری x۸۶–۶۴ اجرا میشود و اثر چکش ردیف را برای دستیابی نامحدود به تمام حافظه فیزیکی نصبشده در یک کامپیوتر، بهرهبرداری میکند. با استفاده از خطاهای مزاحم با پاشش حافظه، این بهرهبرداری قادر به تغییر ورودیهای جدول صفحه (PTE) است[18] که توسط سیستم حافظه مجازی برای نقشهبرداری آدرسهای مجازی به آدرسهای فیزیکی مورد استفاده قرار میگیرد، که نتیجه آن سوءاستفاده از دسترسی نامحدود حافظه میباشد. با توجه به ماهیت آن و عدم توانایی معماری x86-64 در ایجاد clflush یک دستورالعمل ماشین ممتاز، این بهرهبرداری به سختی قابل استفاده در رایانههایی است که از مکانیزمهای جلوگیری از چکش ردیفی داخلی استفاده نمیکنند. Project Zero هنگام آزمایش قابلیت استفاده از سوء استفاده، متوجه شد که حدود نیمی از ۲۹ لپ تاپ آزمایش شده دارای خطاهای مزاحم هستند، در حالی که برخی از آنها در کمتر از پنج دقیقه کپی کردن با چکش ردیفی در لپ تاپهای آسیبپذیر رخ میدهند. لپ تاپهای آزمایش شده بین سالهای ۲۰۱۰ و ۲۰۱۴ ساخته شدهاند و از حافظه غیر ECC DDR3 استفاده میکنند.[2][6][35]

code1a: mov (X), %eax // read from address X mov (Y), %ebx // read from address Y clflush (X) // flush cache for address X clflush (Y) // flush cache for address Y mfence jmp code1a

در ژولای ۲۰۱۵، گروهی از محققان امنیتی مقالهای منتشر کردند که یک روش مبتنی بر معماری و راه مستقل برای بهرهبرداری از اثر چکش ردیفی را توصیف میکند. به جای تکیه بر دستورالعمل clflush برای انجام فلاشهای حافظه نهان، این روش با ایجاد سرعت بسیار بالایی از تخلیه حافظه نهان با استفاده از الگوهای دسترسی دقیق به حافظه، به حافظه غیرمشخص میرسد. اگرچه سیاستهای جایگزینی حافظه پنهان بین پردازندهها متفاوت است، این رویکرد با بکارگیری الگوریتم استراتژی تخلیه حافظه پنهان تطبیقی بر اختلافات معماری غلبه میکند. اثبات مفهوم این رویکرد هم به عنوان اجرای کد بومی و هم به عنوان اجرای جاوا اسکریپت محض که در فایرفاکس ۳۹ اجرا میشود، ارایه شدهاست. اجرای جاوا اسکریپت به نام Rowhammer.js[38] از آرایههای وارد شده بزرگ استفاده میکند و به تخصیص داخلی آنها با استفاده از صفحات بزرگ تکیه دارد؛ در نتیجه، یک سوءاستفاده سطح بسیار بالا از یک آسیبپذیری در سطح پایین را نشان میدهد.[39][40][41][42]

در اکتبر ۲۰۱۶، محققان در سیستمهای VUSec و گروه امنیت شبکه در vu آمستردام DRAMMER را منتشر کردند که یک برنامه اندروید است که از rowhammer با روشهای دیگر استفاده میکند تا بهطور قابلاطمینان دسترسی ریشهای به چند مدل محبوب از گوشی هوشمند را به دست آورند.[43] این آسیبپذیری به عنوان CVE-2016-6728[44] اذعان شد و وصله ای در مدت یک ماه توسط گوگل منتشر شد تا اثر خود را کاهش دهد، اما به دلیل ماهیت کلی اجرایهای احتمالی حمله، وصله نرمافزاری کارآمد دشوار است که بتواند با اطمینان آن را پیادهسازی کند. در حقیقت، تا ژوئن ۲۰۱۸، اغلب پیشنهادهای ارائهشده توسط دانشگاهیان و صنعت برای متوقف ساختن تمام حملات، غیر عملی یا ناکافی بود.[45] برای کاهش این حملات، محققان VUSec Systems یک دفاع سبک را ارائه دادند که با جداسازی بافرهای DMA با ردیفهای محافظ، از حملات مستقر در DMA جلوگیری میکند.[45][46]

همه حالات نرمافزاری در برابر حملات rowhammer آسیبپذیر نیستند. در نتیجه یک مهاجم نیاز به پیدا کردن حالات هدف درست به منظور استفاده از خطاهای rowhammer دارد. در عمل، یکی از چالشهای اصلی شناسایی حالتهای هدف است. این کار بهطور معمول توسط متخصصان حوزه انجام شدهاست. جامعه تحمل نقص اصلی به حملات rowhammer با یک روش اصولی واکنش نشان داد که میتواند برای شناسایی، اعتبارسنجی، و ارزیابی وضعیت هدف حمله rowhammer و بهرهبرداری استفاده شود.[47] این کار مبتنی بر روش تجربی مبتنی بر تزریق خطا است، و به حالتهای هدف حمله عمومی تعمیم داده شد و چند حالت هدف کاربردی پیدا کرد که قبلاً ناشناخته بودند.

منابع

- Kim, Yoongu; Daly, Ross; Kim, Jeremie; Fallin, Chris; Lee, Ji Hye; Lee, Donghyuk; Wilkerson, Chris; Lai, Konrad; Mutlu, Onur (2014-06). "Flipping bits in memory without accessing them: An experimental study of DRAM disturbance errors". 2014 ACM/IEEE 41st International Symposium on Computer Architecture (ISCA). IEEE. doi:10.1109/isca.2014.6853210. ISBN 978-1-4799-4394-4. Check date values in:

|date=(help) - "ECG Response: March 10, 2015". Circulation. 131 (10): 923–924. 2015-03-10. doi:10.1161/circulationaha.115.015716. ISSN 0009-7322.

- Kim, Dae-Hyun; Nair, Prashant J.; Qureshi, Moinuddin K. (2015-01-01). "Architectural Support for Mitigating Row Hammering in DRAM Memories". IEEE Computer Architecture Letters. 14 (1): 9–12. doi:10.1109/lca.2014.2332177. ISSN 1556-6056.

- Yan, Jun (2008-11-07). "Addictive Drugs May Hijack Food's Reward System". Psychiatric News. 43 (21): 10–10. doi:10.1176/pn.43.21.0010. ISSN 0033-2704.

- Carvalho, Agda; Paraguai, Luisa (2015-06-14). "A-thing: body-animal, body-device, body-thing". ARS (São Paulo). 13 (25): 63. doi:10.11606/issn.2178-0447.ars.2015.105523. ISSN 2178-0447.

- Qiao, Rui; Seaborn, Mark (2016-05). "A new approach for rowhammer attacks". 2016 IEEE International Symposium on Hardware Oriented Security and Trust (HOST). IEEE. doi:10.1109/hst.2016.7495576. ISBN 978-1-4673-8826-9. Check date values in:

|date=(help) - Yan, Jun (2008-11-07). "Addictive Drugs May Hijack Food's Reward System". Psychiatric News. 43 (21): 10–10. doi:10.1176/pn.43.21.0010. ISSN 0033-2704.

- Khandelwal, Swati (May 16, 2018). "Nethammer—Exploiting DRAM Rowhammer Bug Through Network Requests". The Hacker News. Retrieved May 21, 2018.

- Gepner, Pawel; Fraser, David L.; Gamayunov, Victor (2012-12). "Performance evaluation of Intel Xeon E5-2600 family cluster using scientific and engineering benchmarks". 2012 2nd IEEE International Conference on Parallel, Distributed and Grid Computing. IEEE. doi:10.1109/pdgc.2012.6449823. ISBN 978-1-4673-2925-5. Check date values in:

|date=(help) - «Original PDF». dx.doi.org. دریافتشده در ۲۰۲۰-۰۷-۱۵.

- dx.doi.org http://dx.doi.org/10.12952/journal.elementa.000074.s001. دریافتشده در ۲۰۲۰-۰۷-۱۵. پارامتر

|عنوان= یا |title=ناموجود یا خالی (کمک) - «Original PDF». dx.doi.org. دریافتشده در ۲۰۲۰-۰۷-۱۵.

- «Original PDF». dx.doi.org. دریافتشده در ۲۰۲۰-۰۷-۱۵.

- Schroeder, Bianca; Pinheiro, Eduardo; Weber, Wolf-Dietrich (2009-06-15). "DRAM errors in the wild". ACM SIGMETRICS Performance Evaluation Review. 37 (1): 193–204. doi:10.1145/2492101.1555372. ISSN 0163-5999.

- Kim, Yoongu; Daly, Ross; Kim, Jeremie; Fallin, Chris; Lee, Ji Hye; Lee, Donghyuk; Wilkerson, Chris; Lai, Konrad; Mutlu, Onur (2014-06). "Flipping bits in memory without accessing them: An experimental study of DRAM disturbance errors". 2014 ACM/IEEE 41st International Symposium on Computer Architecture (ISCA). IEEE. doi:10.1109/isca.2014.6853210. ISBN 978-1-4799-4394-4. Check date values in:

|date=(help) - Kyungbae Park; Sanghyeon Baeg; ShiJie Wen; Richard Wong (October 2014). "Active-precharge hammering on a row induced failure in DDR3 SDRAMs under 3× nm technology". Active-Precharge Hammering on a Row Induced Failure in DDR3 SDRAMs under 3x nm Technology. IEEE. pp. 82–85. doi:10.1109/IIRW.2014.7049516. ISBN 978-1-4799-7308-8.

- Kim, Yoongu; Daly, Ross; Kim, Jeremie; Fallin, Chris; Lee, Ji Hye; Lee, Donghyuk; Wilkerson, Chris; Lai, Konrad; Mutlu, Onur (2014-06). "Flipping bits in memory without accessing them: An experimental study of DRAM disturbance errors". 2014 ACM/IEEE 41st International Symposium on Computer Architecture (ISCA). IEEE. doi:10.1109/isca.2014.6853210. ISBN 978-1-4799-4394-4. Check date values in:

|date=(help) - (PDF) https://www.blackhat.com/docs/us-15/materials/us-15-Seaborn-Exploiting-The-DRAM-Rowhammer-Bug-To-Gain-Kernel-Privileges.pdf. پارامتر

|عنوان= یا |title=ناموجود یا خالی (کمک) - "Tysoe, John Sidney, (14 March 1932–5 Aug. 2015), Chairman, Yorkshire Electricity Group, 1992–94". Who Was Who. Oxford University Press. 2007-12-01.

- "3 is the magic number (of bits): Flip 'em at once and your ECC protection can be Rowhammer'd". www.theregister.com. Retrieved 2020-07-15.

- Zeitouni, Shaza; Gens, David; Sadeghi, Ahmad-Reza (2018-06). "It's Hammer Time: How to Attack (Rowhammer-based) DRAM-PUFs". 2018 55th ACM/ESDA/IEEE Design Automation Conference (DAC). IEEE. doi:10.1109/dac.2018.8465890. ISBN 978-1-5386-4114-9. Check date values in:

|date=(help) - Zeitouni, Shaza; Gens, David; Sadeghi, Ahmad-Reza (2018-06). "It's Hammer Time: How to Attack (Rowhammer-based) DRAM-PUFs". 2018 55th ACM/ESDA/IEEE Design Automation Conference (DAC). IEEE. doi:10.1109/dac.2018.8465890. ISBN 978-1-5386-4114-9. Check date values in:

|date=(help) - Kim, Dae-Hyun; Nair, Prashant J.; Qureshi, Moinuddin K. (2015-01-01). "Architectural Support for Mitigating Row Hammering in DRAM Memories". IEEE Computer Architecture Letters. 14 (1): 9–12. doi:10.1109/lca.2014.2332177. ISSN 1556-6056.

- "JEDEC". JEDEC (formerly the GaAs REL Workshop) ROCS Workshop, 2004. IEEE. 2004. doi:10.1109/rocs.2004.184332. ISBN 0-7908-0105-1.

- «Original PDF». dx.doi.org. دریافتشده در ۲۰۲۰-۰۷-۱۵.

- "Analysis and Study of Vulnerability Scanning Result for Projects within Organization". March 29-30, 2015 Singapore. Universal Researchers. 2015-03-29. doi:10.17758/ur.u0315212. ISBN 978-93-84468-20-0.

- Marc Greenber (March 9, 2015). "Row Hammering: What it is, and how hackers could use it to gain access to your system". synopsys.com. Retrieved January 10, 2016.

- Jung, Sang chul (2014-10-26). "The Analysis of strategic Management of Samsung Electronics Company through the Generic Value chain Model". Science & Engineering Research Support soCiety. doi:10.14257/astl.2014.63.15.

- "JEDEC". JEDEC (formerly the GaAs REL Workshop) ROCS Workshop, 2004. IEEE. 2004. doi:10.1109/rocs.2004.184332. ISBN 0-7908-0105-1.

- «data sheet 1.pdf». dx.doi.org. دریافتشده در ۲۰۲۰-۰۷-۱۵.

- Nishad Herath; Anders Fogh (August 6, 2015). "These are Not Your Grand Daddy's CPU Performance Counters: CPU Hardware Performance Counters for Security" (PDF). Black Hat. pp. 29, 38–68. Retrieved January 9, 2016.

- "Seven days: 27 February–5 March 2015". Nature. 519 (7541): 10–11. 2015-03. doi:10.1038/519010a. ISSN 0028-0836. Check date values in:

|date=(help) - Enstrom, Emma; Kreitz, Gunnar; Niemela, Fredrik; Soderman, Pehr; Kann, Viggo (2011-10). "Five years with kattis — Using an automated assessment system in teaching". 2011 Frontiers in Education Conference (FIE). IEEE. doi:10.1109/fie.2011.6142931. ISBN 978-1-61284-469-5. Check date values in:

|date=(help) - Niels Provos; Markus Friedl; Peter Honeyman (August 10, 2003). "Preventing Privilege Escalation" (PDF). niels.xtdnet.nl. Retrieved March 11, 2015.

- "Griffin, Liam, (born 9 March 1973), Vice Chairman, Addison Lee Ltd, since 2015". Who's Who. Oxford University Press. 2015-12-01.

- Murat Balaban (June 6, 2009). "Buffer Overflows Demystified" (TXT). enderunix.org. Retrieved March 11, 2015.

- Page, Jason S. (2013-06-04). "Boildown Study on Supernatant Liquid Retrieved from AW-106 in December 2012".

- Daniel Gruss; Clémentine Maurice (July 27, 2015). "IAIK/rowhammerjs: rowhammerjs/rowhammer.js at master". github.com. Retrieved July 29, 2015.

- https://arxiv.org/abs/1507.06955. پارامتر

|عنوان= یا |title=ناموجود یا خالی (کمک) - "Beckett, Lt Gen. Thomas Anthony, (born 28 July 1962), Defence Senior Adviser to the Middle East, since 2015; Security Envoy to Kurdistan Region of Iraq, since 2015". Who's Who. Oxford University Press. 2010-12-01.

- Jean-Pharuns, Alix (July 30, 2015). "Rowhammer.js Is the Most Ingenious Hack I've Ever Seen". Motherboard

- Goodin, Dan (August 4, 2015). "DRAM 'Bitflipping' exploit for attacking PCs: Just add JavaScript". Ars Technica.

- Stenz, Ronald; Dong, Xiquan; Xi, Baike; Feng, Zhe; Kuligowski, Robert J. (2016-01-27). "Improving Satellite Quantitative Precipitation Estimation Using GOES-Retrieved Cloud Optical Depth". Journal of Hydrometeorology. 17 (2): 557–570. doi:10.1175/jhm-d-15-0057.1. ISSN 1525-755X.

- Byers، Robert؛ Waltermire، David؛ Turner، Christopher (۲۰۲۰-۰۲-۱۰). «National Vulnerability Database (NVD) Metadata Submission Guidelines for Common Vulnerabilities and Exposures (CVE) Numbering Authorities (CNAs) and Authorized Data Publishers». dx.doi.org. دریافتشده در ۲۰۲۰-۰۷-۱۵. کاراکتر line feed character در

|عنوان=در موقعیت 38 (کمک) - van der Veen, Victor; Lindorfer, Martina; Fratantonio, Yanick; Padmanabha Pillai, Harikrishnan; Vigna, Giovanni; Kruegel, Christopher; Bos, Herbert; Razavi, Kaveh (2018), "GuardION: Practical Mitigation of DMA-Based Rowhammer Attacks on ARM", Detection of Intrusions and Malware, and Vulnerability Assessment, Springer International Publishing, pp. 92–113, doi:10.1007/978-3-319-93411-2_5, hdl:1871.1/112a5465-aeb5-40fd-98ff-6f3b7c976676, ISBN 978-3-319-93410-5

- "RAMPAGE AND GUARDION - Vulnerabilities in modern phones enable unauthorized access". Retrieved June 30, 2018.

- Yim, Keun Soo (2016-09). "The Rowhammer Attack Injection Methodology". 2016 IEEE 35th Symposium on Reliable Distributed Systems (SRDS). IEEE. doi:10.1109/srds.2016.012. ISBN 978-1-5090-3513-7. Check date values in:

|date=(help)