کاهیدگی سد با واداشتن درین

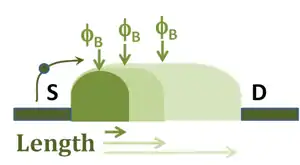

کاهیدگی سد با واداشتن درین (DIBL) یک اثر کانال کوتاه در ماسفت است که در اصل به کاهش ولتاژ آستانه ترانزیستور در ولتاژ تخلیه بالاتر اشاره دارد. در یک ترانزیستور اثر میدان مسطح سنتی با کانال بلند، گلوگاه در تشکیل کانال به اندازه کافی دور از اتصال درین اتفاق میافتد که بهصورت الکترواستاتیک با استفاده از زیرلایه و گیت از درین محافظت میشود و به همین ترتیب کلاسیک ولتاژ آستانه مستقل از ولتاژ درین بود. در ادوات کانال-کوتاه، دیگر صحیح نیست: درین به اندازه کافی نزدیک گیت است تا کانال را ببندد، بنابراین یک ولتاژ تخلیه بالا میتواند گلوگاه را باز کرده و زودتر ترانزیستور را روشن کند.

منشأ کاهش آستانه را میتوان به عنوان یک نتیجه از خنثیسازی بار دانست: مدل تقسیم بار یاو.[1]

با کاهش طول کانال، اثرات DIBL در ناحیه زیرآستانه (وارونگی ضعیف) در ابتدا به عنوان یک ترجمه ساده از منحنی جریان زیرآستانه برحسب بایاس گیت با تغییر در ولتاژ درین ظاهر میشود، که میتواند به عنوان یک تغییر ساده در ولتاژ آستانه با بایاس درین مدلسازی شود. با این حال، در طولهای کوتاهتر شیب منحنی جریان در مقابل بایاس گیت کاهش مییابد، یعنی نیاز به یک تغییر بزرگتر در بایاس گیت برای تأثیر همان تغییر در جریان درین دارد. در طولهای بسیار کوتاه، گیت کاملاً نمیتواند قطعه را خاموش کند. این اثرات را نمیتوان به عنوان تنظیم آستانه مدلسازی کرد.[2]

در عمل، DIBL میتواند به صورت زیر محاسبه شود:

که یا Vtsat ولتاژ آستانهای است که در یک ولتاژ منبع تغذیه (ولتاژ درین بالا) اندازهگیری شده، و یا Vtlin ولتاژ آستانهای است که در ولتاژ درین بسیار کم اندازهگیری میشود، بهطور معمول ۰٫۰۵ ولت یا ۰٫۱ ولت. ولتاژ منبع تغذیه (ولتاژ درین بالا) و ولتاژ درین کم (برای یک قسمت خطی از مشخصات IV قطعه) است. منهای جلوی فرمول مقدار DIBL مثبت را تضمین میکند.

DIBL میتواند فرکانس کاری قطعه را نیز کاهش دهد، همانطور که در معادله زیر شرح داده شدهاست:

که ولتاژ منبع تغذیه است ولتاژ آستانه است

منابع

- Narain Arora (2007). Mosfet Modeling for VLSI Simulation: Theory And Practice. World Scientific. p. 197, Fig. 5.14. ISBN 981-256-862-X.

- Yannis Tsividis (2003). Operation and Modeling of the MOS Transistor (Second ed.). New York: Oxford University Press. p. 268; Fig. 6.11. ISBN 0-19-517014-8.