منطق انماس

منطق نیمرسانا فلز اکسید - نوع ان از نیمرساناهای نوع N برای پیادهسازی گیتهای منطقی و سایر مدارهای دیجیتالی استفاده میکند. این گونه ترانزیستورهای از نوع انماس، با ایجاد یک لایه وارونگی در بدنه ترانزیستورهای نوع p کار میکنند. این لایه وارونگی، کانال n نامیده میشود، میتواند الکترون را ین پایانههای «منبع» و «تخلیه» نوع n هدایت کند. کانال n با اعمال ولتاژ به پایه سوم که «گیت» نامیده میشود ایجاد میشود. مانند سایر ماسفتها، ترانزیستورهای انماس دارای چهار نوع عملکرد هستند: قطع (cut-off) (یا زیر آستانه)، تریودی، اشباع (که گاهی اوقات «فعال» نامیده میشود) و اشباع سرعت.

بررسی اجمالی

MOS مخفف نیمرسانا فلز اکسید است، که بیان کننده این امر است که ساخت ترانزیستورهای MOS، عمدتاً قبل از دهه ۱۹۷۰، با دروازههای فلز، بهطور معمول آلومینیوم، ساخته میشد. با این وجود، از حدود سال ۱۹۷۰، بیشتر مدارهای MOS از دروازههای خود تراز ساخته شده از سیلیکون پلی کریستال استفاده کردهاند، این فناوری اولین بار توسط فدریکو فاگین در فرچایلد سمیکانداکتر توسعه داده شد. این دروازههای سیلیکونی هنوز در اکثر انواع مدارهای مجتمع مبتنی بر ماسفت مورد استفاده قرار میگیرند، اگرچه دروازههای فلزی (از جنس Al یا Cu) در اوایل سال ۲۰۰۰ برای انواع خاصی از مدارهای پر سرعت مانند ریزپردازندههای با کارایی بالا بار دیگر مورد استفاده قرار گرفتند.

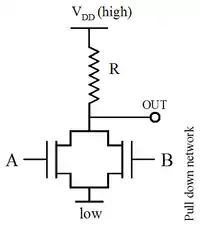

ماسفتها ترانزیستورهای حالت تقویت از نوع n هستند که در یک شبکه به اصطلاح «کششی» (شبکه پایین-کش) بین خروجی دروازه منطقی و ولتاژ منبع منفی (نوعاً زمین) تعبیه شدهاند. یک بالا-کش (یعنی «باری» که میتوان آن را مانند یک مقاومت در نظر گرفت، در شکل زیر ببینید) بین یک منبع مثبت و تک تک خروجیهای دروازه منطقی قرار میگیرد. هر گیت منطقی، از جمله اینورتر منطقی، میتواند با طراحی شبکه ای از مدارهای موازی یا سری پیادهسازی شود، به این ترتیب که اگر خروجی مورد نظر برای ترکیبی خاص از مقادیر ورودی بولی، صفر (یا نادرست) باشد، PDN فعال خواهد بود، به این معنی که حداقل یک ترانزیستور مسیر فعلی جریان بین منبع منفی و خروجی را اجازه میدهد. این باعث افت ولتاژ بار و در نتیجه ولتاژ پایین در خروجی میشود که نشان دهنده صفر است.

به عنوان مثال، در اینجا یک دروازه NOR پیادهسازی شده در انماس شماتیک وجود دارد. اگر ورودی A یا ورودی B زیاد باشد (منطق ۱، = درست)، ترانزیستور ماس مربوطه مانند یک مقاومت بسیار کم بین خروجی و منبع منفی عمل میکند و خروجی را مجبور میکند که دارای مقدار کم باشد (منطق ۰، = نادرست). وقتی A و B هر دو بالا باشند، هر دو ترانزیستور رسانا هستند و حتی یک مسیر با مقاومت پایینتر از قبل به سمت زمین ایجاد میکنند. تنها حالتی که خروجی زیاد است زمانی است که هر دو ترانزیستور خاموش باشند؛ که فقط در صورت کم بودن A و B رخ میدهد، بنابراین جدول زیر درستی یک دروازه NOR را ارضا میکند:

| A | B | A NOR B |

|---|---|---|

| ۰ | ۰ | ۱ |

| ۰ | ۱ | ۰ |

| ۱ | ۰ | ۰ |

| ۱ | ۱ | ۰ |

میتوان یک MOSFET را طوری ساخت که همچون یک مقاومت عمل کند، بنابراین کل مدار را میتوان فقط با ماسفتهای کانال n ساخت. مدارهای انماس در انتقال پایین به بالا کند عمل میکنند. هنگام انتقال از بالا به پایین، ترانزیستورها مقاومت کمی ایجاد میکنند و بار خازنی در خروجی خیلی زود تخلیه میشود (شبیه تخلیه خازن از طریق یک مقاومت بسیار ضعیف). اما مقاومت بین خروجی و منبع مثبت بسیار بیشتر است، بنابراین انتقال کم به زیاد بیشتر طول میکشد (شبیه به شارژ یک خازن از طریق یک مقاومت قوی). استفاده از مقاومت با مقدار کم، روند را تسریع میکند اما باعث اتلاف توان استاتیک میشود. با این حال، یک روش بهتر (که متداولترین روش نیز هست) برای سریعتر شدن گیتها استفاده از ترانزیستورهای حالت تخلیه به جای ترانزیستورهای حالت بهبود به عنوان بار است. این منطق انماس کاهش بار نامیده میشود.

تا مدتها، مدارهای انماس بسیار سریعتر از مدارهای پیماس و سیماس قابل مقایسه با یکدیگر، که مجبور بودند از ترانزیستورهای کانال p بسیار کندتر استفاده کنند، بودند. همچنین ساخت انماس از سیماس آسانتر بود، زیرا دومی مجبور یود تا ترانزیستورهای کانال p را در چاههای ویژه n بر روی زیرلایه p پیادهسازی کند. اشکال عمده در مورد انماس (و اکثر خانوادههای منطقی) این است که جریان DC باید حتی زمانی که خروجی در حالت ثابت است بی بایست از یک درگاه منطقی عبور کند (در مورد انماس کم است). این به معنای اتلاف توان استاتیک است، یعنی تخلیه برق حتی در صورت عدم تغییر مدار. یک وضعیت مشابه در مدارهای مدرن با سرعت بالا، که مدارهای سیماس با چگالی بالا (ریزپردازندهها و غیره) و که دارای کشش جریان استاتیک قابل توجهی نیز هستند، نیز رخ میدهد. اگرچه این به دلیل نشت است، نه بایاس. با این وجود، مدارهای استاتیک سیماس قدیمی یا کندتر که برای ایاسآیسی، اسرم و غیره استفاده میشوند، معمولاً مصرف برق استاتیک بسیار کمی دارند.

علاوه بر این، دقیقاً مانند DTL، TTL، ECL و غیره، سطح منطق ورودی نامتقارن باعث میشود که مدارهای انماس و پیماس نسبت به سیماس بیشتر در معرض نویز و خطا باشند. به سبب این معایب است که منطق سیماس امروزه بیشتر این نوعها را در اکثر مدارهای دیجیتال پرسرعت مانند ریزپردازندهها جایگزین کردهاست (با وجود این که سیماس در اصل در مقایسه با دروازههای منطقی ساخته شده با ترانزیستورهای دو قطبی بسیار کند بود).